#背景

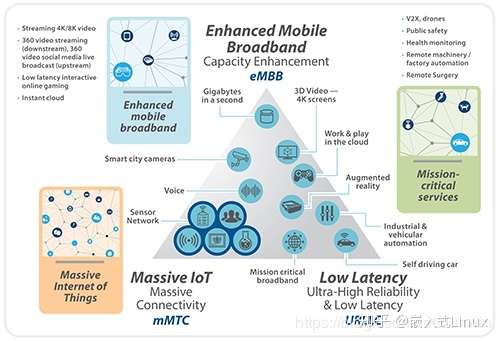

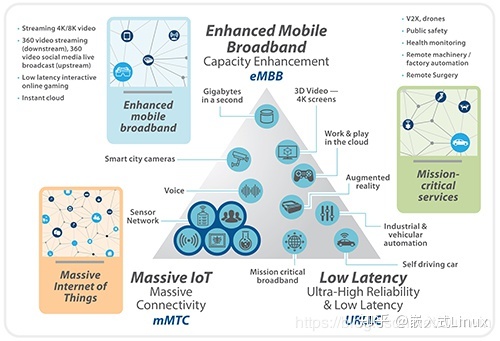

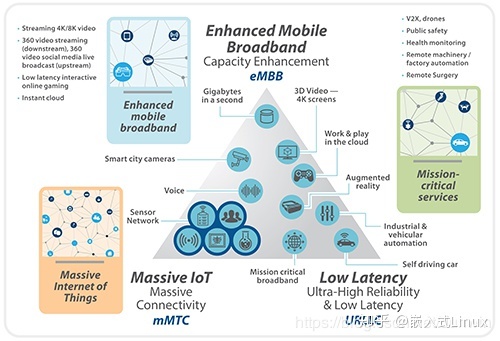

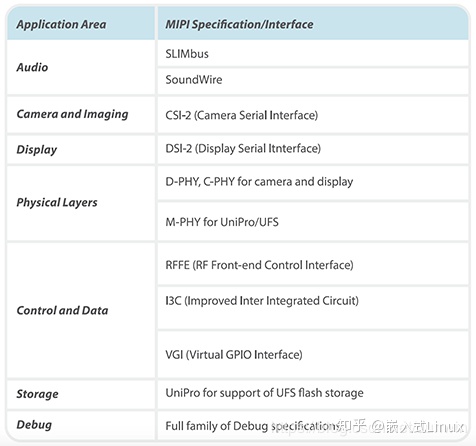

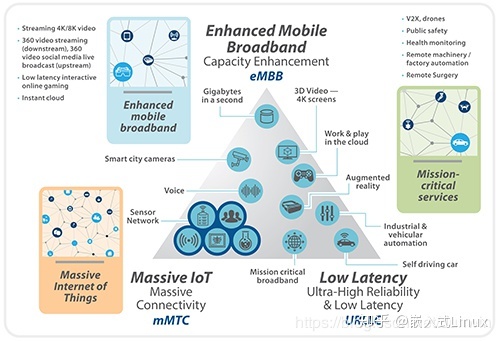

2020年 是5G元年,很多行业因5g重新定义。显示行业也不例外,针对5G,mipi联盟发表了对应的白皮书 描述了现有的MIPI规范如何能够支持代5G智能手机以及其他新兴的5G移动平台,包括互联/自动/半自动车辆和物联网(IoT)设备.

本文图片来之mipi与其他网站

#mipi 5G中优势

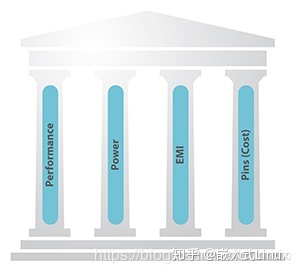

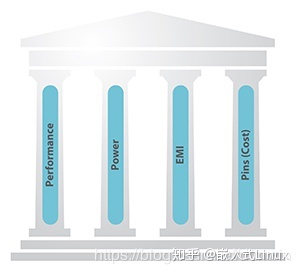

- 高性能 MIPI接口可在应用程序处理器和相机等组件之间提供高速和低传输延迟。通过使用MIPI规范,系统设计人员不必担心接口将成为破坏用户体验的瓶颈。高性能对于5G设备尤为重要,因为用户希望它们比4G和3G型号更快,响应更快。

- 引脚数少 高性能是MIPI规范旨在大程度地减少引脚数的一种方式。例如,MIPI PHY中的高性能以及低速MIPI I3C和VGI接口中的高效协议可将AP和外围设备中的引脚数小化。降低复杂性还可以降低设备成本,从而为他们提供更大的可寻址销售市场,尤其是在价格高度敏感的物联网领域。

- 低电量 MIPI规范的设计具有很高的能源效率,这对于提供人们希望从智能手机和可穿戴设备获得的较长电池寿命至关重要。例如,MIPI接口通过多种因素组合来降低EMI,这些因素包括高速PHY(C-PHY,D-PHY,M-PHY)上的低电压摆幅,所有低速CMOS接口(1.2V)的适应性( (例如RFFE和I3C),目前的电平为1.8V,并严格支持这些规格的摆率控制。

- EMI 设备越小,组件之间的空间越小。如此接近意味着更高的EMI风险,这会损害设备的性能和可靠性。

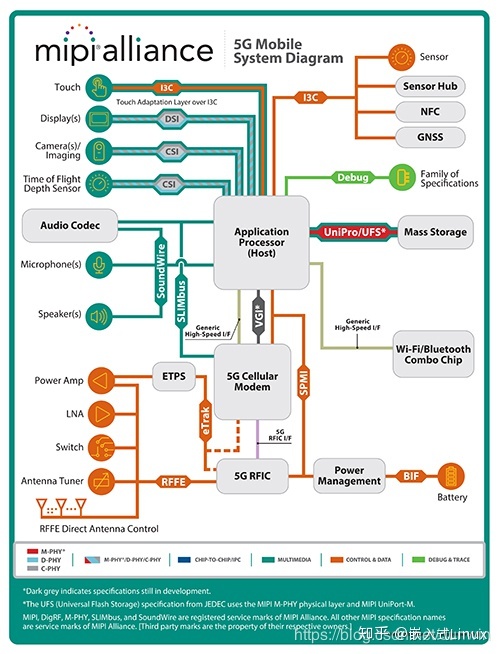

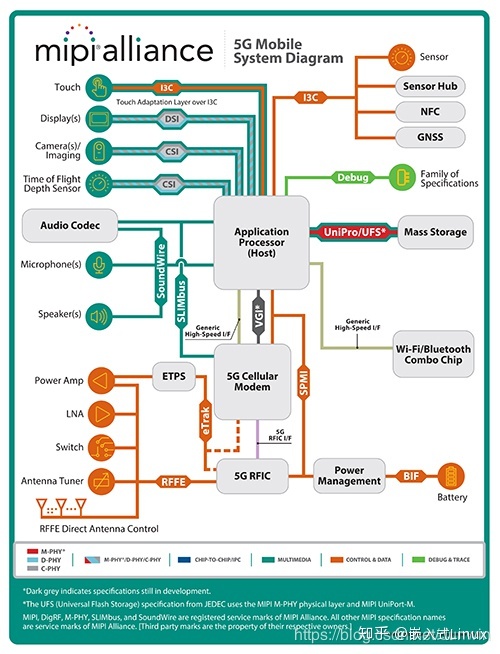

#5G手机中的mipi

5G智能手机可能具有三到四个具有高帧率/慢动作视频捕获功能的高分辨率后置摄像头,增强型麦克风阵列,多声道音频和立体声扬声器。 5G调制解调器和应用处理器使用MIPI规范,例如相机的CSI-2和显示器的DSI-2,以及低功耗,高带宽,引脚效率高的MIPI D-PHY或C-PHY物理层。在5G设计中,用于RF前端设备控制的MIPI RFFE和带有M-PHY的MIPI UniPro用于高性能闪存存储都变得无处不在。MIPI I3C,SoundWire,SLIMbus和即将发布的VGI规范也有望在许多即将发布的5G智能手机平台中采用。

#mipi

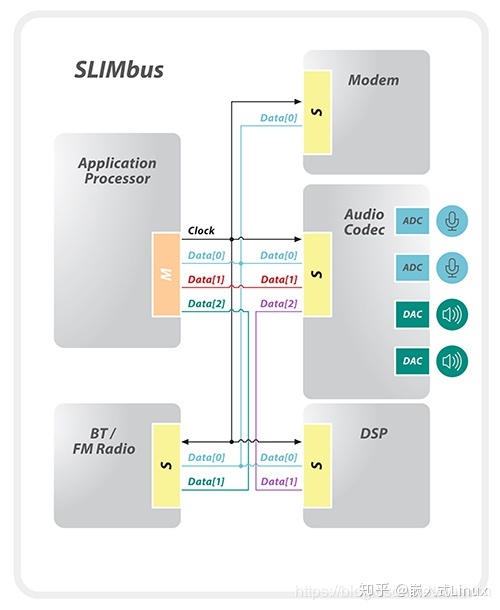

#1. MIPI SLIMbus和SoundWire

提供丰富,逼真的音频和逼真的通话。 MIPI音频工作组定义了两个规范:MIPI SLIMbus和MIPI SoundWire。这些接口简化了多种平台中多个音频组件的集成,包括智能手机,PC,联网车辆,可穿戴设备和IoT设备。 MIPI SLIMbus主要设计用于在较大的组件之间传输音频。举例说明了与外围设备(例如蓝牙,FM和音频子系统/编解码器)接口的调制解调器和应用处理器等示例。 SLIMbus v2.0是两线制,多分支TDM接口,支持多主机和多个设备。它采用以高达28MHz的单数据速率(SDR)运行的CMOS I / O,具有固定的帧大小,支持主控和时钟切换功能,以实现低功耗操作。SLIMbus v2.0还支持多个多通道,高质量音频流,相位相干性,以实现立体声,麦克风阵列和其他引人注目的功能。它还支持每台设备多八个通道的可扩展带宽,以使峰值聚合带宽高达到224Mbps。

MIPI SoundWire是MIPI SLIMbus的补充规范。SoundWire于2014年推出,整合了移动和PC行业音频接口中的关键属性,并提供了一种通用的,可扩展的体系结构,可用于在各个细分市场的多种类型的设备中启用全面的音频功能。

MIPI SoundWire是一个统一接口,主要用于小型音频外围设备。它针对低复杂度,低门数设计进行了优化,以支持在手机中使用成本敏感的音频组件,例如数字麦克风,数字扬声器和放大器。此外,它可以优化扬声器保护,麦克风功率和性能,噪声消除以及“始终听”音频输入。

SoundWire具有许多SLIMbus功能。SoundWire v1.1还采用CMOS I / O,并支持多达11个从设备,多通道音频,PDM格式以及带内控制/中断/唤醒。但是,它以高达12.288MHz(高达24.576 Mbps)的双数据速率(DDR)模式运行,并支持可配置的帧大小和增强的低延迟协议。多达8个数据通道的可选多通道扩展可用于支持高端音频应用。例如,八通道192 KHz 24位音频需要8 * 24 * 192000 = 36.864 Mbps,这将需要两个或更多通道,而它可能以较低的频率运行以相应地优化功率。

通过SoundWire直接连接到多个数字麦克风和扬声器的应用处理器的示例。 MIPI SoundWire和MIPI SLIMBus可以通过桥接解决方案在系统中协同运行,从而为移动或受移动平台影响的平台提供灵活而复杂的音频系统。

简而言之: MIPI SLIMbus和SoundWire准备支持代5G智能手机。SLIMbus是具有成熟音频组件的成熟规范,已部署在智能手机和受移动设备影响的平台中。SoundWire作为高端智能手机平台中的数字麦克风和扬声器的推动者正在迅速获得发展势头

#2. MIPI CSI-2

MIPI CSI-2是几乎所有4G LTE智能手机中的主要摄像头接口,并且已经在批5G智能手机中使用。MIPI CSI-2规范通过多摄像头,深度摄像头(ToF)和面部检测传感器支持灵活的移动设计。当今的主流手机多可支持两个背面传感器,而某些型号则具有三个。明天的5G设备将配备带Tele + Wide,Color + Mono,Main + Depth传感器的两个传感器,或上述三传感器配置的两个传感器+眼睛/面部检测/ ToF传感器。与MIPI D-PHY或C-PHY物理层耦合的MIPI CSI-2可以支持所有这些实现。

基于C-PHY v1.2的CSI-2 v2.1可通过每条通道的三条线上提供高达8.0 Gbps(每秒3.5 Giga符号或Gsps)的嵌入式时钟和数据,并支持通道扩展(其中三个通道可达到24 Gbps)使用九根线的C-PHY通道)CSI-2还支持D-PHY v2.1通过四根导线提供高达4.5 Gbps的转发时钟和数据,并支持数据通道扩展(使用10根导线可达到18 Gbps)。

智能手机中的主摄像头当前为12-16MP,某些型号高达100MP。随着现在4K / 30fps视频捕获的普遍使用,到2021年左右,4K / 120fps和8K / 30fps视频捕获可能会变得可用。即使使用高色彩深度RAW20,CSI-2 v2.1也已经可以支持这些高分辨率和帧速率组合。 (8K x 30fps x 20位/ RAW像素= 20 Gbps)。它们还处于下一代CSI-2和C-PHY / D-PHY数据速率的能力之内。

但是CSI-2不仅仅是分辨率,帧速率和带宽。MIPI相机工作组将继续推动功能,以增强新兴的5G用例,例如AI /机器视觉,AR / VR和联网车辆。这些功能包括:

- 延迟降低传输效率(LRTE),以减少传输延迟,促进实时感知,处理和决策;并优化运输效率,以减少导线数量,触发速率和功率。

- 眼动追踪(AVRET),摄像机到摄像机同步,AV / VR应用程序的摄像机显示同步。

- 感兴趣的智能区域(SRoI)支持分布式视觉和混合视觉架构。

- USL(统一串行链接)有助于促进对物联网产品平台的本地长距离支持。

- RAW 12-10-12压缩/解压缩减少了带宽,同时为任务关键型视觉应用提供了无压缩伪影的出色信噪比(SNR)图像。

- RAW-16,RAW-20和RAW-24色深可提供卓越的图像质量,极大地改善了场景内的高动态范围(HDR)和SNR以实现高质量的成像,并可以为自动驾驶汽车和AI系统带来“视觉”功能。

- 增强的CCI(摄像机控制接口)和CCS(摄像机命令集)支持I2C FM +和MIPI I3C SDR和HDR_DDR模式,以实现更高的吞吐量,更低的延迟摄像机控制。

- 加扰和SSC(扩频时钟-仅MIPI D-PHY)可降低功率谱密度(PSD)的发射并使无线电干扰小化。

MIPI CSI-2支持各种不同分辨率,帧速率,质量和色深的低成本和高质量图像传感器。选择和功能的结合使它成为有时被称为“移动++”设备的流行选择。示例包括AR / VR耳机,无人机和IoT端点。

汽车OEM及其供应商经常将MIPI CSI-2用于需要统一的端到端成像以及近实时处理和决策的应用。MIPI摄像头工作组目前正在计划优化的MIPI摄像头解决方案,以支持严格的汽车环境和某些IoT用例:

- 对映射到汽车或物联网平台(例如,无人机)的长距离通道的本地支持。

- 统一串行链路(USL),保证为关键任务(例如,自动驾驶汽车)应用传输

- 同步图像传感器以实现视觉应用

- 提供端到端安全性(例如,交错式AES-256)

简而言之: MIPI CSI-2规范是4G应用程序的接口,从智能手机到无人机再到连接的车辆。这种偏好一直持续到5G,其中CSI-2已经从智能手机开始支持波5G设备。2021年市场的CSI-2规范将包含新的带宽/分辨率和功能,并支持多相机,深度感应,LRTE,USL,AVRET,SRoI,RAW-16 / -20 / -24 ,具有I2C_FM +和I3C支持的增强型CCI。所有这些功能将极大地增强5G移动设备的移动用户体验。

#3. MIPI DSI-2

智能手机的显示分辨率和每英寸像素(PPI)一直在不断增加,

为了应对这一趋势,MIPI显示工作组与VESA的显示流压缩(DSC)任务组合作。MIPI DSI v1.2在2014年采用了VESA DSC标准,可提供高达4:1、8 bpp的视觉无损压缩。MIPI Alliance和VESA继续合作。例如,在2018年5月,DSI-2 v1.1采用了新的VESA VDC-M标准,可提供高达5:1、6 bpp的视觉无损压缩。MIPI C-PHY v1.2上的DSI-2 v1.1高可提供8.0 Gbps(3.5 Gsps)的嵌入式时钟和数据,每条通道3条线上,并支持通道扩展(使用3条C-PHY通道可达到24 Gbps)九根电线)。这等效于具有3条C-PHY v1.2通道的每个DSI链路的8.0 Gbps x 3 C-PHY通道x 5 = 120 Gbps有效带宽。DSI-2 v1.1还支持D-PHY v2.1多交付4个。

智能手机的显示分辨率预计不会超过4K或5K分辨率(屏幕尺寸分别为5.5英寸时分别为800和1000 PPI),而平板电脑和笔记本电脑的分辨率则不会超过8K或10K分辨率(572和715 PPI时高为15.4英寸)甚至超过2021年)。主要原因是,许多研究表明,要达到如此高的分辨率在技术上都非常困难,而且在如此高的PPI情况下,其视觉质量的提升也将有限或没有。DSI-2 v1.1已支持这些分辨率和带宽,它满足并超过了2021年以后的新要求。同时,DSI-2还有效地减少了物理带宽,同时使设备设计能够成本更低,由于导线更少而体积更小,电池寿命更长。

MIPI DSI-2也是许多AR / VR显示设备的事实选择,例如头戴式显示器(HMD)和眼镜。5G将带来更好和更丰富的AR / VR用户体验,这将需要更好的HMD显示器。研究人员正在努力减少所谓的“ VR疾病”,这可能是通过添加某种形式的头部和/或眼睛跟踪传感器,显示和音频同步以及其他技巧来避免对人脑的感官冲突。MIPI规范现已准备就绪,可以启用这些功能(,以帮助解决VR疾病。

MIPI显示工作组将继续调查5G的含义和潜在的增强功能,例如高带宽,低延迟的返回通道,以支持和丰富新兴的5G用例。

简介: MIPI DSI-2当前是世界上使用广泛的接口,用于4G智能手机和其他具有更高分辨率和PPI要求的显示器的设备。MIPI显示工作组不断增强DSI-2的能力,以满足新兴市场的需求,例如与VESA的显示流压缩(DSC)任务组合作,提供高达5:1、6 bpp的视觉无损压缩。这些举措和其他举措还确保DSI-2非常适合启用5G智能手机,AR / VR HMD和其他具有更要求的设备。

#4. MIPI D- / C- / M- / A-PHY

MIPI提供了三个高性能和成本优化的物理层规范系列:D-PHYSM,M-PHY和C-PHYSM。MIPI D-PHY已经成为当今部署的主要PHY层,几乎在所有4G LTE智能手机中都与CSI-2和DSI-2耦合。同时,与MIPI UniPro / JEDEC UFS配对的M-PHY是当今LTE设备和批5G智能手机中的高性能移动存储接口。凭借新的MIPI CSI-2和DSI-2规范以及行业支持,预计C-PHY的采用也会迅速增加。

MIPI D-PHY是移动行业中部署广泛的低功耗物理层。D-PHY针对MIPI CSI-2摄像机和DSI / DSI-2显示协议进行了优化,可提供高性能,低功耗和低EMI,使其与移动设备中的复杂RF子系统兼容。D-PHY v2.1高支持4.5 Gbps /通道,并使用10条线(利用4条数据通道和一条时钟通道)支持数据通道扩展,使总数据速率达到18 Gbps。

MIPI C-PHY通过带宽受限的通道提供高吞吐量性能,可将显示器和摄像机连接到应用处理器。C-PHY通过使用在三线通道上实现〜2.28位/符号的三相符号编码,在两线通道上偏离传统的差分信令技术来实现这一点。每个通道都包含一个嵌入式时钟。C-PHY v1.2支持高达3.5 Gsps / lane,相当于8 Gbps / lane,并且可以在三个通道上实现24 Gbps的峰值带宽。

MIPI M-PHY是一个性能驱动的通用物理层,针对多媒体,高性能存储和芯片间互连用例。它使用带有嵌入式时钟的差分信号,支持具有不同位信号和时钟方案的两种传输模式,以及多个高速齿轮,为性能和功耗之间的运行时优化提供配置选择。M-PHY v4.1支持11.6 Gbps /通道,四个通道的总带宽为46.4 Gbps。

M-PHY通常与MIPI UniPro协议结合使用,该协议支持JEDEC的通用闪存(UFS)。作为可靠,高性能的传输,低功耗和低延迟链路。UFS v2.1已经成为高性能4G智能手机中主要的移动存储,并且还将部署在代5G智能手机中。同时,UFS v3.0将通过充分利用M-PHY v4.1性能功能,继续为5G时代的旗舰设备提供先进的移动存储。MIPI M-PHY还是MIPI CSI-3,MIPI DigRF,MIPI LLI和MIPI UniPro协议的PHY。

MIPI PHY系列规范已支持5G。请参阅第3.1.2、3.1.3和3.1.8节,以了解更多有关当前D-PHY v2.1,C-PHY v1.2和M-PHY v4.1规范如何超过业界2021+性能和带宽的信息。要求。

MIPI PHY工作组将继续推动下一代PHY规范的发展,以满足2024+ 5G的需求,以适应新的5G用例,并瞄准物联网和汽车等“超越移动”应用。即将发布的C-PHY v2.0和D-PHY v3.0规范分别针对高达6 Gsps / lane和14 Gbps / data lane的数据速率。他们还旨在通过比移动外形设备更长的通道来支持物联网用例,同时保留MIPI PHY的优势,以提供低功耗,低延迟和低EMI解决方案。此外,正在讨论新的M-PHY规范,该规范的目标是大约23 Gbps / lane的数据速率以及降低的等待时间,从而变得更加节能。也可以通过编码方案来提高效率。

MIPI还致力于解决汽车在环绕传感器以及显示应用中的用例。由于MIPI协议已被相机传感器和显示器广泛采用,因此MIPI还希望为汽车链接提供一种解决方案,以将此类设备连接至中央处理器。随着MIPI A-PHYSM物理层规范的发展(可以满足12-24 Gbps)的要求,需求收集已经开始支持更高的速度,包括用于显示和其他用例的超过48 Gbps。完成后,这些规范将满足5G时代汽车行业未来的连接需求。

MIPI A-PHY v1.0预计将于2019年底面向开发人员提供。该规范将优化布线,成本和重量要求,因为高速数据,控制数据和可选电源共享同一条物理布线。MIPI A-PHY链路的非对称特性,其点对点拓扑结构以及对移动协议世代的重用保证了开发人员和汽车OEM总体上较低的复杂性,功耗和系统成本。预计首批使用A-PHY组件的车辆将在2024年投入生产。除了汽车用途外,该规范的配置还将非常适合物联网和工业等应用。

简而言之: MIPI D-PHY,M-PHY和C-PHY是4G设备以及批智能手机中高性能,成本优化的物理层规范的事实上的标准。它们巧妙地平衡了市场对显示器和摄像头等应用的带宽,延迟和功耗要求,同时为OEM提供了选择余地。即将对MIPI现有PHY和新的MIPI A-PHY进行的增强将使MIPI移动协议的世代能够适应汽车,物联网和其他新兴用例。